#### **MODULATORS**

R. W. Bradford, P. C. Edwards, C. W. Olson, Editor, R. M. Rowe, W. T. Tomlin, F. T. Veldhuizen, and A. L. Williams

This chapter describes two pulse modulators developed for the SLAC accelerator. The first is the "main modulator," one of which is associated with each high-power klystron. The second is the "sub-booster modulator," one of which is located in each of the thirty sectors of the machine to pulse a sub-booster drive klystron.

#### 13-1 Main modulator

History (CWO)

During the initial design phase, several different types of modulators were considered. The one selected and built for the accelerator was the line-type modulator. This was chosen not only because of its high efficiency and relatively low cost but also because of the large reservoir of practical experience on the line-type modulator which had accumulated at Stanford during the development of klystrons and earlier accelerators.

The original concept was to use eight large power supplies, each of which would be rated at approximately 3 MW output at 23 kV and would furnish do on a common buss to thirty modulators. Each modulator was to have a fuse and a switch to disconnect it from the line for maintenance purposes. In addition, each modulator was to have a vacuum relay to remove it rapidly from the common do buss in the event of switch tube faults. A power scavenging de-Q'ing system was to be included for fast regulation of the pulse-forming network voltage. Induction voltage regulators were to be used to regulate output voltage by feedback to the ac input.

Because spark gaps were not very reliable at 360 pulses/sec and would,

consequently, require considerable maintenance, the switching device considered for use in the modulators was the multigrid, mercury pool ignitron. No large single hydrogen thyratron capable of handling the specified power levels (65-MW peak, 75-kW average output) existed at that time. Initially, the ignitron appeared to be a good solution, but experiments revealed serious disadvantages such as excessive fault rate, excessive anode time delay, low holdoff voltage, short life, and complicated triggering. During the period of experimental work with ignitrons, the state of the art for hydrogen thyratrons was advancing, and, by 1963, tubes which would satisfy our requirements became available.

That same year, the large megawatt power supply concept was re-evaluated with respect to high-voltage stability during switch tube faults. It was recognized that large switch tubes will occasionally fault. During such occurrence a short circuit would be placed on the 23-kV supply. Although a vacuum relay would be incorporated to clear such faults, the buss voltage supplying the remaining twenty-nine modulators would vary during the fault duration. This would, in turn, cause the output of the modulators to change and klystron phase shift and power decrease to occur. A direct consequence of this phase shift and decrease in RF power would be degradation of the beam energy spectrum. This problem and the inflexibility of adjusting the voltage of individual modulators to compensate for different klystron perveances resulted in changing the design concept from large dc power supplies feeding many modulators to small ones for each modulator.

In the adopted system, ac power at 12.47 kV is fed the length of the accelerator into induction voltage regulators which step this voltage down to a selected value between 258 and 595 V. Each induction voltage regulator supplies ac power to sixteen modulators. This system provides improved isolation from modulator to modulator, better fault clearing because ac faults are easier to clear than dc faults, and the capability of making minor voltage adjustments on each modulator by changing primary taps on the local rectifier transformer to compensate for different klystron perveances.

## General description (CWO)

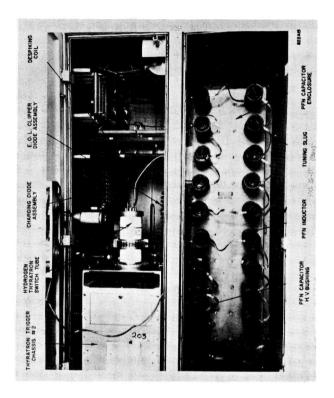

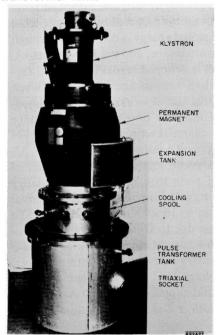

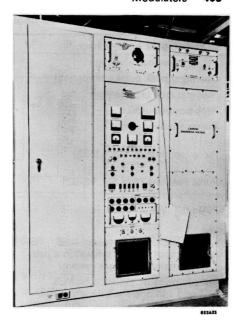

The modulator built for the two-mile accelerator, shown in Figs. 13-1 and 13-2, was designed by SLAC personnel and fabricated and assembled from SLAC-supplied drawings and specifications.

The modulator and its associated pulse transformer was designed to meet or exceed the performance specifications given in Table 13-1.

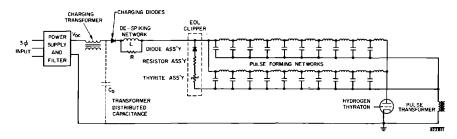

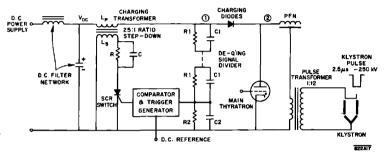

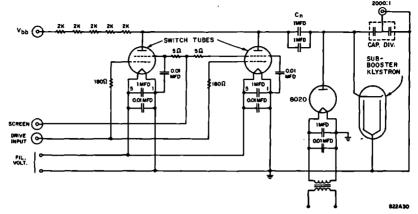

The SLAC modulator is called a "line-type modulator." It is so named because it uses a capacitance-inductance network (pulse-forming network) constructed so as to simulate electrically a transmission line. A simplified diagram of the modulator is shown in Fig. 13-3. The main pulse and charging circuits have been drawn in schematic form to aid in the explanation of these circuits.

Figure 13-1 The SLAC modulator, view 1.

After each output pulse, the pulse-forming network (PFN) capacitors charge to approximately twice the dc power supply voltage because of the resonant charging characteristics of the charging transformer and the total PFN capacitance. The charging current flows from power supply ground, through the primary of the pulse transformer, the PFN inductors, the charging diodes, and the charging transformer to the positive side of the dc power supply. Because of the low values of inductances of the pulse

822A2

Table 13-1 Overall specifications of modulator (including pulse transformer)

| Peak power output (max)                          | 65 MW                                    |

|--------------------------------------------------|------------------------------------------|

| Average power output (max)                       | 75 kW                                    |

| Output pulse voltage range                       | 150–250 kV                               |

| Output pulse current range                       | 110–262 A                                |

| Load impedance range                             | 1365–955 ohms                            |

| Pulse length, flat top                           | $2.5\mu\mathrm{sec}$                     |

| Rise time                                        | $0.7\mu\mathrm{sec}$                     |

| Fall time                                        | $1.2\mu\mathrm{sec}$                     |

| Pulse repetition rates                           | 360, 180, 120, 60 pulses/sec             |

| Pulse height deviation from flatness (max)       | $\pm$ 0.5%                               |

| Pulse amplitude drift<br>Long term<br>Short term | $\pm$ 1.5%/hour $\pm$ 0.25%/5-min períod |

| Time jitter                                      | $\pm$ 10 nsec                            |

transformer primary and the PFN inductors, they have negligible effect on the charging cycle.

The PFN capacitor retains the voltage level of nearly twice the dc power supply voltage until the hydrogen switch tube is triggered. Once this occurs the PFN capacitors discharge through the primary of the pulse transformer, the switch tube, and PFN inductors. Since the reflected impedance of the klystron into the pulse transformer primary is approximately equal to the characteristic impedance of the PFN, half of the voltage on the PFN capacitors appears across the pulse transformer and half is dropped across the

MAIN MODULATOR EOL CLIPPER CHARGING CHARGING TRANSFORMER D. C. POWER SUPPLY DeQing SIGNAL SCR SWITCH DeQing Chassis | 8.2 DeQina REF. PEN DRIVER VOLTAGE HYDROGEN THYRATRON SWITCH TRIGGER TRIGGER CHASSIS # TRIGGER CHASSIS # 2 KLYSTRON 120 V PULSE TRANSF CORE BIAS POWER SUPPLY 60 cps KLYSTRON FILAMENT SUPPLY

837A

Figure 13-3 Block diagram of modulator.

PFN. The time for complete discharge of the PFN is approximately 3.5  $\mu$ sec. Once the discharge is complete, the positive plate voltage on the hydrogen thyratron extinguishes and conduction ceases.

In addition to the main pulse and charging circuits described above there are additional supporting circuits as shown in Fig. 13-3. Trigger chassis Nos. 1 and 2 receive the input trigger pulse and shape and amplify it to the value required to trigger the hydrogen thyratron switch tube.

The de-Q'ing chassis in conjunction with the silicon controlled rectifier (SCR) switch and the charging transformer regulates the value of the charge placed on the PFN. If this charge were allowed to vary, the subsequent output pulse to the klystron would, in turn, be affected. Without some form of regulation any short-term ac line variations would show up as changes in the output of the dc supply which would cause the network charge and output voltage to vary accordingly.

The de-Q'ing circuitry regulates as follows. The PFN voltage is sampled by means of a voltage divider. This PFN voltage analog is fed to the comparator together with a dc reference voltage. The dc reference voltage is also fed to the variable voltage substation (VVS), where it sets the level of the ac voltage fed to the modulators. When the sampled PFN voltage exceeds the dc reference voltage, the comparator generates an output pulse which is shaped by the driver chassis to trigger the SCR. The energy left in the charging transformer at the time the SCR conducts is dissipated in the secondary load resistor. The reverse blocking action of the charging diode causes the PFN voltage to be maintained at the value it had when the de-Q'ing circuit fired.

The de-Q'ing circuit is normally adjusted to dissipate a few percent of the charge in each cycle. It can, on a pulse-to-pulse and long-term basis, regulate the PFN voltage to 0.1% for line voltage changes of 3% or less, and for any repetition rate from 60 to 360 pulses/sec. Also, since the ac voltage from the VVS tracks the de-Q'ing reference voltage, the de-Q'ing system stays within range for all modulator output voltages.

A klystron filament power supply and a pulse transformer core bias supply are also included within the modulator. The output of both can be adjusted by controls and monitored by meters at the modulator's control panel.

The design, with the exception of the de-Q'ing circuitry, was patterned after conventional line-type modulators. Ideas from previous modulators procured from industry and from previous Stanford units were utilized.

The choice of the main high-voltage level in the modulator was governed by several factors. The major one was the ratings of the available switch tubes, which at the time the modulator was being designed, was 50 kV. In order to get the required rise time out of the pulse transformer, it was necessary to keep the turns ratio as low as possible. The klystron requires a maximum of 250 kV on its cathode. Therefore, using a turns ratio of 1:12, the modulator is required to produce a pulse of 21 kV. This pulse voltage demands about 40 kV maximum on the pulse-forming network which gives a comfortable margin with

50-kV thyratrons. Since the Q of the charging system is high, there is approximately 2:1 step-up in voltage from power supply to pulse-forming network. The power supply voltage required is, therefore, 20 kV plus about 3% for de-Q'ing. Approximately 5% "positive" mismatch is used at full voltage, i.e., the load impedance is about 5% higher than the PFN impedance.

The cabinet which measures 4 ft wide  $\times$  8 ft deep  $\times$  8 ft high is built of heavy gauge sheet steel. Three doors are provided on each long side to provide easy access to all components inside. Cooling for the components inside the cabinet is provided by three 1500-ft<sup>3</sup>/min fans mounted just below exhaust ports in the roof of the modulator.

Radio frequency interference (RFI) was recognized as a problem because of the high pulse voltages involved. Precautions are taken to minimize RFI originating from high-energy pulse radiation. The cabinet is divided into two parts, the high and the low noise regions, with a steel bulkhead separating the two. As much of the low level circuitry as possible is placed in the low noise part so as to minimize RFI pickup on its wiring. The doors are equipped with RFI metal gasketing so as to form good conductive seals around the door edges. In addition, latches are provided around the edges of the doors to force them against the gasketing thus providing better conduction between mating parts. The air intakes and exhaust ports are covered with RFI filters of the honeycomb type to prevent radiation through these openings. All wires, ac and control leads, passing through the top of the cabinet are filtered with RFI filters to reduce conducted noise.

The control panel contains all the necessary controls, meters, and interlock lights to operate the modulator. The main circuit breaker on the left control panel is used for fault protection as well as for connecting and disconnecting the modulator from the main feeder buss which feeds fifteen additional modulators. The modulator is sufficiently stable to make run-up from low voltage unnecessary. It may be placed on the line at any VVS voltage setting within the operating range. For maintenance purposes, an auxiliary power input socket on the left control panel, just above the air intake, is used to supply power to the modulator from a portable power source. Access to this socket is made by unlatching its protective cover with the same key that, upon removal, locks out the main circuit breaker. This provides personnel protection and, in addition, prevents simultaneous excitation from two power sources.

The lethal voltages present within the modulator when the unit is operating made it mandatory to incorporate a number of personnel safety features. The modulator has a total of six lock-equipped doors. The key for five of these doors is located inside the modulator on the support post adjacent to the left rear door. The key for the latter door is attached by welded ring to another key normally inserted into a key interlock mounted on the front control panel. In order to remove the two keys it is necessary to rotate the key interlock to the "off" position. This electrically opens the interlock and prevents excitation of the high voltage. When the left rear door is opened, a spring-loaded two sectional high-voltage shorting switch closes and places a short across the

filter and PFN capacitors. In addition, a door microswitch in series with the five remaining door interlocks releases and electrically opens the interlock chain. Grounding hooks are also provided inside each door with an attached cable that drapes across the door opening to remind the individual gaining access to use the hook to ground out any potentially hazardous circuits.

It was recognized early in the design phase that each modulator-klystron station would be subject to various faults during operation, such as klystron arcs, vacuum system gas bursts, thyratron faults, high-voltage power supply overloads, and end-of-line clipper overcurrents. A circuit was incorporated in the modulator interlock chain which works in conjunction with an external klystron protection chassis. It recycles the modulator up to a predetermined number of faults (from 1 to 15 as set by a rotary switch on the control panel) in 55 min. If the actual faults exceed the predetermined number in the 55-min period, the modulator is shut down automatically and must be reset manually. Faults external to the modulator merely interrupt the trigger for approximately 1 sec or longer in case of continuous faults. Faults originating in the modulator interrupt the high voltage by opening a contractor in the primary of the main rectifier transformer. If the fault clears in 1.5 sec, the high voltage is turned on automatically and operation is resumed.

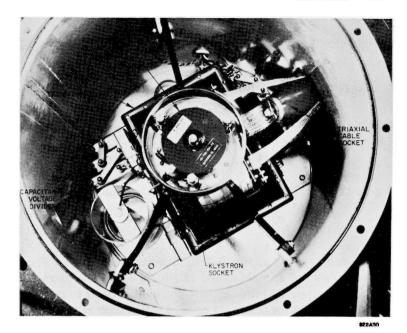

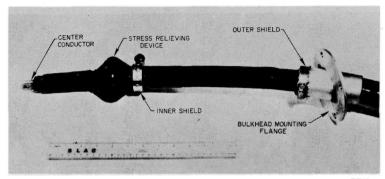

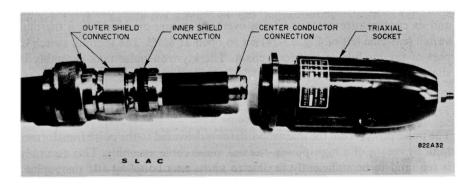

As can be seen in Fig. 13-2, the pulse transformer tank is external to the modulator cabinet and is an appendage hanging from the bottom of the klystron. A special triaxial cable feeds the pulse power from the modulator to the pulse transformer tank.

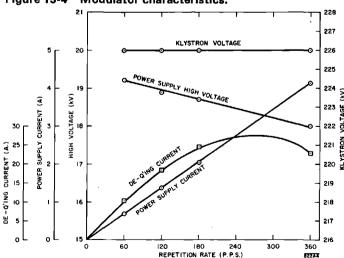

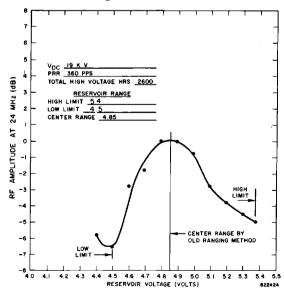

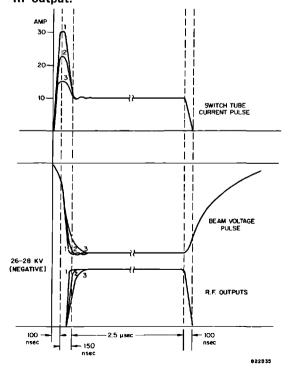

Figure 13-4 shows modulator-characteristic curves of the dc power supply output voltage and current, the de-Q'ing current, and the klystron beam voltage for various pulse repetition rates.

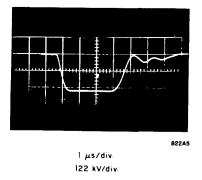

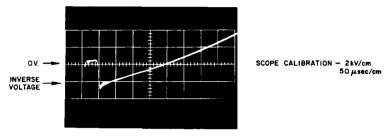

Figure 13-5 is an oscillogram of the klystron beam voltage pulse.

Figure 13-4 Modulator characteristics.

Figure 13-5 Klystron beam voltage pulse. (Time scale: 1 µsec/large division.)

## Modulator power supplies (PCE)

The three-phase ac input to the modulator can be any level from 258 to 595 V, depending on the setting of the external induction voltage regulator. This regulator furnishes the ac power to a total of sixteen modulators. The input ac enters the modulator through three 125-A line filters which decouple high-frequency noise from the ac lines, thus preventing possible RFI.

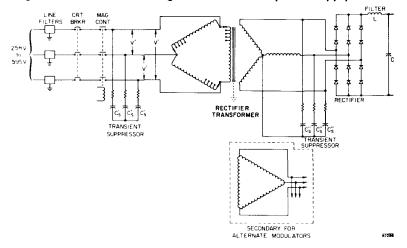

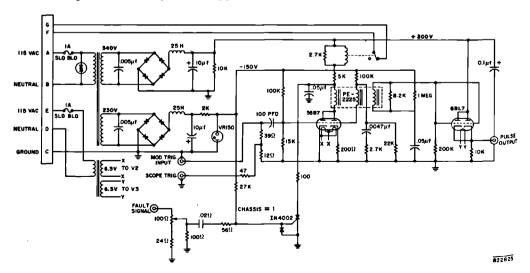

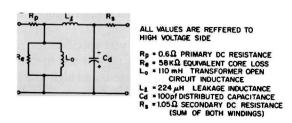

The power supply used in the modulator is a conventional, three-phase, double-way, dc power supply. The three-phase variable voltage is delivered through a circuit breaker and contactor to a step-up rectifier transformer (see Fig. 13-6). The secondary of this transformer feeds power to a semiconductor rectifier assembly. The rectified output, proportional to the ac input, is delivered to the pulse-forming network via the inductance-capacitance (*LC*) rectifier filter and charging transformer.

Figure 13-6 Schematic diagram of modulator power supply.

The rectifier transformer is an oil-filled, hermetically sealed, floor-mounted unit. It is rated to provide 3.8 A (rms) at 17.3 kV with 595 V in the primary. The primary has taps brought out to external terminals to allow reduction of dc output voltage in steps of 2.5, 5, 7.5, and 10%. The dc regulation is 8% (maximum) for a range from 5 to 100% full load. The reactance of the transformer was selected to be  $10 \pm 0.75\%$ . This fairly high leakage reactance was chosen to limit the load current during short circuit faults in order to protect rectifier units from damage. The transformer excitation does not exceed 5% at 595 V.

The secondary of the rectifier transformer is connected to a three-phase, double-way, semiconductor rectifier assembly. This assembly consists of six stacks of 100 silicon diodes, each capable of delivering 3 A average at 600 V. Each diode is paralleled with a resistance and a capacitor to equalize voltage distribution across the series string. The entire rectifier assembly is rated to deliver 23 kV at 4.5 A dc when the modulator is running at the maximum repetition rate of 360 pulses/sec.

The rectifier transformers for half of the 240 modulators are connected with a delta primary and a delta secondary while the remainder are connected delta—Y. The result is a phase shift in the harmonic currents of one group with respect to the other. The characteristic fifth and seventh harmonics of a sixphase rectifier effectively cancel one another.

Low-frequency transient suppressor networks are connected from line to line in the primary and secondary of the rectifier transformer. These suppressors not only reduce transients resulting from rectifier commutation action in the secondary but also prevent the occurrence of overvoltage caused by the interruption of exciting current in the primary.

If these transients are not suppressed, damage to the solid-state rectifier assembly can occur, and dielectric insulation failure can result from the repetition of transient overvoltages caused by the action of rectifier commutation. The capacitors in the primary suppressor are sized to maintain the transformer exciting current magnitude by resonating with the transformer's inductance at a frequency not greater than 60 cycles/sec for a short period after the primary voltage is disconnected from the transformer by opening the line circuit breaker. The transformer excitation and primary transient suppressor capacitor circuits are analyzed as follows:

1. The transformer excitation equivalent inductance for  $\Delta$  winding connection is calculated from

$$L_e' = \sqrt{3} V' / 2\pi f I_e$$

where

$L_e$  = the equivalent inductance of the transformer excitation circuit in henrys

$I_e$  = the exciting current measured in the supply lines, rms amperes

V' = the supply line to line voltage, rms volts

f =the frequency (= 60 Hz)

2. The primary line to line suppressor capacitance,  $C_{s}'$  is calculated from

$$C'_{s} = [(2\pi f)^{2} L'_{e}]^{-1}$$

farads

The primary side suppressor circuit is connected in Y (with the neutral isolated). Therefore each capacitance has to be twice the value calculated from (2) above. The voltage rating of the capacitors is 660 V ac in order to provide sufficient safety factor. The transformer core loss serves as a damping feature for  $L'_eC$ , so that only a nominal value of resistance is needed in series with the suppressor capacitance to provide proper damping.

Transients due to rectifier commutation tend to cause ringing in the secondary circuit comprising the transformer winding leakage inductance and the coil inherent capacitance. The purpose of the secondary suppressors is not only to reduce this ringing frequency but also to damp the transient oscillation by the insertion of series resistance. Because resistance cannot be placed in a load current circuit, it is included in series with the capacitor. The secondary circuit is connected in Y with the neutral isolated. Thus, the suppressor is a series resistance—capacitance network shunted across the 17-kV lines. Analysis of the secondary circuit includes the following steps:

1. The capacitance  $C_2$ , reflected into the secondary from the suppressor capacitance  $C'_s$  in the primary, is given by

$$C_2 = \frac{2C_s'}{N^2}$$

where N = the secondary-to-primary turns ratio.

2. The secondary suppressor capacitance  $C_s''$  is calculated from

$$C'' = [(2\pi f_1)^2 L_s'']^{-1}$$

and

$$C_s = [(2\pi f_0)^2 L_s'']^{-1}$$

where

C'' = the total capacitance formed by  $C_2$  in series with the parallel combination of the suppressor capacitance  $C_s''$  and  $C_s$

$L_s''$  = the equivalent transformer leakage inductance in henrys

$C_s$  = the coil inherent equivalent capacitance in farads

$f_1$  = the desired ringing frequency in hertz

$f_0$  = the natural frequency of the coil in hertz

Note that the transformer inherent frequency is typically 10-50 kHz, and  $C''/C_s = (f_0/f_1)^2$ . In order to reduce  $f_1$  by one order of magnitude to avoid frequencies within the  $L_s''C_s$  frequency bandwidth, the ratio  $C''/C_s$  has to be 100:1. The value of the damping resistance is calculated using  $R_s = 2(L_s''/C'')^{1/2}$  ohms, where  $R_s$  is the series damping resistance including the transformer equivalent copper load loss resistance.

The LC filter in the dc circuit performs two functions. It attenuates the 360-Hz rectifier ripple to an acceptable value and reduces the ac power line

| Pulse<br>repetition  |     |     |     | For h | armonic | freque | ncy (H | z) <i>:</i> |      |              |

|----------------------|-----|-----|-----|-------|---------|--------|--------|-------------|------|--------------|

| rate<br>(pulses/sec) | 120 | 180 | 240 | 300   | 420     | 660    | 780    | 1380        | 1500 | Total<br>rms |

| 360                  | 0.3 | 0.5 |     | 0.7   | 0.5     | 0.2    | 0.2    | 0.8         | 0.6  | 1.5          |

| 180                  | 0.4 | 0.4 | 0.3 | 0.4   | 0.2     | 0.1    | 0.1    | 0.4         | 0.3  | , 1.2        |

| 60                   | 8.0 | 0.3 | 0.2 | 0.3   | 0.2     | _      |        | 0.2         | 0.2  | 1.1          |

Table 13-2 Alternating current power-line harmonic currents at master substation

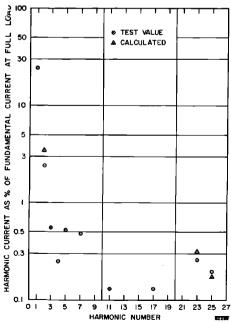

harmonics, which result from resonant charging of the modulator PFN to less than 3% (total rms) of full modulator line current. The largest harmonic current occurs at 120 Hz when the modulator is operating at 60 pulses/sec.

The ac power line harmonic currents associated with operation of the accelerator are individually less than 1% of the fundamental (60-Hz) line current when the modulator is operating at full load. Table 13-2 lists the harmonics resulting from accelerator runs at 360, 180, and 60 pulses/sec. The maximum of all the harmonics is 1.5% rms and occurs at 360 pulses/sec. These harmonics flowing in the power system source impedance produce a 3% distortion of the line frequency sine wave. This amount of distortion is acceptable from the standpoint of interference with communications and control systems.

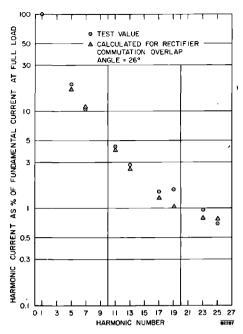

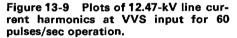

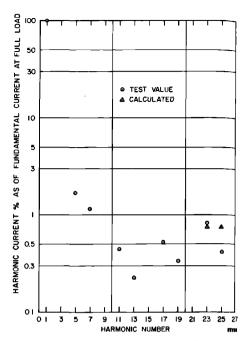

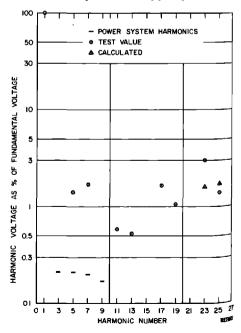

Typical harmonic current characteristics of an individual modulator are shown in Fig. 13-7. The result of using delta-delta and delta-Y transformer connections together with a phase-shifting transformer in the variable voltage substation is shown in Figs. 13-8 and 13-9. These circuit arrangements and the 12.47-kV cable itself attenuate the harmonic currents so that the master substation carries only a small fraction of the harmonics generated by the individual rectifiers in each modulator. This can be seen by comparing Table 13-2 with Fig. 13-7. Typical harmonic voltages in the 12.47-kV distribution system that result from operating the modulators at 360 pulses/sec are shown in Fig. 13-10.

The total power demand of the modulator system when operating at a level which produces 20-GeV beam energy at 360 pulses/sec is 20.4 MW as listed in Table 13-3. The wattless reactive component required to supply core excitation for the VVS induction voltage regulators as well as that resulting from the rectifier commutation phase angle lag is 10.4 MVAR. Table 13-3 lists the overall accelerator power loads typical for various repetition rates. The power demand load for klystron gallery conventional facilities and auxiliaries is less when the klystrons are operating at 360 pulses/sec than it is when they are being pulsed at 180 or 60 pulses/sec because the waveguide heaters shut off when the heating from RF system losses is sufficient to

<sup>&</sup>quot; Harmonic current expressed as percent of 60-Hz full load current at 360 pulses/sec.

Figure 13-7 Individual modulator ac line-current harmonics.

Figure 13-8 Plots of 12.47-kV line current harmonics at VVS input for 360 pulses/sec operation.

Figure 13-10 Plots of 12.47-kV line voltage harmonics at variable voltage substation input for 360 pps operation.

| Table 13-3   | Alternating current power requirements |

|--------------|----------------------------------------|

| at master so | ubstation for 20 Gev                   |

| Pulse<br>repetition<br>rate<br>(pulses/sec) |                                             | Power<br>Ioad<br>(kW) | Reactive<br>Ioad<br>(KVAR) |

|---------------------------------------------|---------------------------------------------|-----------------------|----------------------------|

| 360                                         | Modulators (240) (ref. 105 V) plus injector | 20,400                | 10,400                     |

|                                             | Klystron gallery conventional facilities    | 4,141                 | 1,900                      |

|                                             | Total                                       | 24,541                | 12,300                     |

| 180                                         | Modulators (240) (ref. 105 V) plus injector | 10,600                | 6,530                      |

|                                             | Klystron gallery conventional facilities    | 5,128                 | 1,870                      |

|                                             | Total                                       | 15,728                | 8,400                      |

| 60                                          | Modulators (240) (ref. 105 V) plus injector | 3,700                 | 3,300                      |

|                                             | Klystron gallery conventional facilities    | 5,128                 | 1,870                      |

|                                             | Total                                       | 8,828                 | 5,170                      |

Not including cable or power factor correction capacitance.

hold the temperature. At 360 pulses/sec and 105 V reference the VVS output voltage is 502 V, the current is 92 A, and the power demand is 75 kW per modulator.

# Pulse-forming network (ALW)

The pulse applied to the high-power klystron is specified to be a maximum of 250 kV at 262 A, with a rise time of 0.7  $\mu$ sec, a fall time of 1.2  $\mu$ sec, and a duration of 2.5  $\mu$ sec, during which time the voltage is to be constant within  $\pm 0.5\%$ . The pulse is supplied by a pulse transformer, which is driven by the modulator.

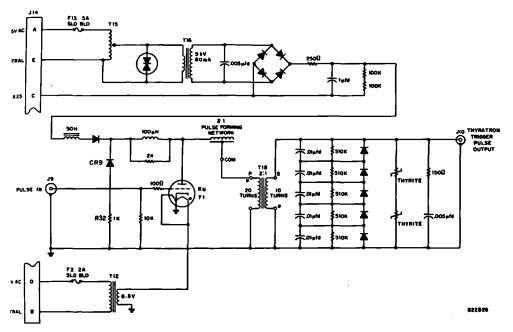

To drive the primary of the pulse transformer, a two-terminal device, the PFN, is used. The PFN simulates the characteristics of a transmission line by the use of lumped capacitive and inductive elements. The PFN used in this modulator is a modified type-E circuit consisting of two parallel networks of ten fixed-value capacitors and ten essentially uncoupled slug-tuned inductors (see Fig. 13-11).

Figure 13-11 Schematic diagram of simplified modulator.

The PFN stores energy in the capacitors at a slow rate and discharges it rapidly in the form of a rectangular pulse of short duration when the hydrogen thyratron is triggered. The duration of the pulse and its approach to an ideal rectangular shape depends on the circuit constants of the PFN.

Although the circuit values of the individual LC sections for a particular pulse shape can be derived theoretically, it is much simpler to start off with the total value of capacitance and inductance required and experimentally derive the individual values. In a strictly theoretical approach, it is difficult to account for parameters such as stray capacitance and inductance that are always present in an actual circuit. In the PFN of this modulator, the total capacitance was derived from the energy equation below which states that the energy stored in the PFN before discharge must equal the energy supplied to the load, i.e.,

$$\frac{1}{2}CV_{c}^{2} = \int_{0}^{T} V_{p}I_{p} dt$$

$$C = \frac{2V_{p}I_{p}T}{V_{c}^{2}}$$

(13-1)

or

where

C = the total PFN capacitance

$V_c$  = the voltage across PFN capacitance (41.6 kV)

$V_p$  = the pulse transformer primary voltage (20.8 kV)

$I_p$  = the pulse transformer primary current (3000 A)

$\dot{T}$  = the duration of pulse (3.35  $\mu$ sec, which includes the equivalent duration of rise and fall times).

The total inductance is found from the PFN characteristic impedance equation, viz.,

$$Z_0 = \left(\frac{L}{C}\right)^{1/2} \tag{13-2}$$

The choice of individual capacitance and inductance values and their number is influenced by previous knowledge of PFN characteristics. Pulse rise time is dependent on the number of LC sections. The greater the number, the faster the rise time. The way the leading edge turns into the flat top is mainly controlled by the value of the inductance nearest the switch tube. A comparatively large value for this coil rounds off the top of the leading edge. Small values give a sharp overshoot which trails off into the flat top. Flat-top irregularities are smoothed out by adjusting for symmetry between LC sections.

In this modulator it was determined that a dual ten-section PFN with fixed capacitors of approximately 0.014  $\mu$ F and tunable inductors of a

maximum inductance of 4.5  $\mu$ H would satisfy the pulse requirements. The dual section PFN was initially used in a split configuration, one section for each of two smaller switch tubes. When the large single switch tube became available, the two PFN's were paralleled. Had the single tube been available during the early design phase, a single ten-section PFN, with larger capacitors, would have been used. The use of tunable inductors allows adjustment over discrete portions of the output pulse. Pulse characteristics such as duration, rise time, droop, flat-top ripple, and fall time can be varied in a coarse manner by locating the interconnecting strap to the desired coil turn, and fine adjustments are made by varying the depth of insertion of a copper-tuning slug in the coil.

The fixed capacitors are specified to be between 0.013 and 0.015  $\mu$ F and 50-kV operating voltage. The dielectric and impregnant used in these capacitors are polyethylene and silicone oil, respectively. The losses with these materials were found to be approximately one-third the losses in equivalent paper—oil capacitors.

The tunable inductors are mounted on the capacitor's high-voltage bushing stud. The inductor consists of ten turns of  $\frac{3}{8}$ -in. o.d. copper tubing with a center-to-center spacing of 4 in. and a length of 7 in. A three-fingered spacer of molded insulating material is mounted inside the inductor and supports a  $2\frac{1}{2}$ -in. diameter,  $5\frac{1}{8}$ -in. long, tubular copper slug. Each of the capacitor-inductor assemblies are interconnected by braided straps, one end of which is attached to the capacitor high-voltage bushing and the other end to the inductor using a cable clamp. Figure 13-12 shows the PFN installed in the modulator.

The PFN can be adjusted while the modulator is operating by installing in the modulator door opening a protective Lucite—wire screen. A Lucite tuning rod with a protective grounding ring midway along its length can be inserted through holes in this screen to adjust the copper tuning slugs.

# End-of-line clipper (ALW)

The end-of-line clipper consists of a series combination of diodes, power resistors, and Thyrite resistors. (See Fig. 13-11.) The entire assembly is connected across the last (farthest removed from the switch tube) PFN capacitor. The function of the end-of-line clipper is to provide a low-impedance load for the collapsing field of the PFN inductors after a klystron fault. Without the end-of-line clipper, the excess energy on the PFN inductors would be transferred as an inverse charge to the PFN capacitors. Such a negative charge on the capacitors would have two adverse effects. The thyratron switch tube could be damaged by reverse arc-through and the PFN capacitors could be over voltaged (in the absence of de-Q'ing) during the next charging cycle. While accomplishing the objective of preventing a high inverse voltage being placed on the PFN capacitors after a load fault, the end-of-line clipper must present essentially an open circuit to the normal PFN positive charge and also

Figure 13-12 Pulse-forming network, installed.

present a high impedance to the low inverse voltage required for thyratron deionization.

The diode section of the end-of-line clipper consists of a series string of one hundred and fifty resistance-capacitance (RC)-compensated, 600-V, 20-A silicon diodes. These diodes provide a low-impedance path for inverse voltages and essentially an open circuit to the normal PFN positive voltage.

The resistor assembly comprises four parallel legs of two 10-ohm, 200-W resistors in series to give an equivalent resistance of 5 ohms. These resistors along with the Thyrite assembly provide essentially a matched power dissipating load to the PFN for the high inverse charge.

The Thyrite assembly is made up of four parallel legs of six 6-in. diameter Thyrite disks in series. Thyrite is a nonlinear resistive material in which the resistance varies inversely as a power function of the voltage. With a negative deionization voltage of say, 3.6 kV the resistance of this Thyrite assembly is approximately 2 kohms. When the high negative fault voltage is impressed on the Thyrite assembly, the resistance drops to an extremely low value, and the

series combination of diodes, power resistors, and Thyrites provides a low impedance to dissipate the negative charge on the PFN. A monitoring device consisting of a current transformer-relay combination senses end-of-line clipper current each time a load fault occurs. In this event, the recycle circuit mentioned earlier in this chapter causes the modulator to be turned off for approximately 1.5 sec and then turned on again.

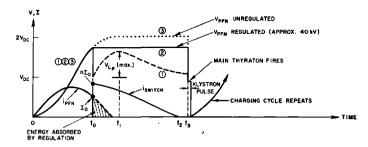

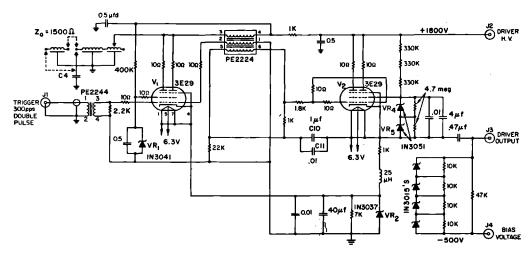

# Pulse-forming network voltage regulation (de-Q'ing) (WTT)

Regulation of the klystron pulse voltage is accomplished by controlling the voltage to which the PFN is charged. This method, although somewhat indirect, is much simpler than working directly with the 250-kV klystron pulse. It has the disadvantage, however, that the actual regulation occurs sometime prior to pulsing the klystron, and leakage in the PFN capacitors or external leakage paths across the network will allow the PFN voltage to discharge slightly. In the SLAC modulators, operating from 60 to 360 pulses/sec, the time delay between regulation and pulsing varies from approximately 14.7 to 0.75 msec. As the discharge or leakage rate is constant, regulation is not affected at fixed repetition rates. The PFN voltage and, consequently, the klystron voltage will decrease slightly, however, when the repetition rate is changed from 360 to 60 pulses/sec.

Regulation against two causes of PFN voltage variation is necessary to insure klystron pulse stability. As the PFN voltage is a direct function of the dc power supply voltage (Eq. 13-5) and this, in turn, is proportional to the ac input voltage, any change in the input is reflected as a change in the PFN voltage. Although the modulators are fed in groups of sixteen by an induction voltage regulator, this unit has a minimum response time of several seconds and cannot regulate for pulse-to-pulse amplitude variations. The second need for regulation arises from either misfiring of the main thyratron during the charging cycle or arcing in the load during the output pulse. Either will result in an increase in PFN voltage for the succeeding charging cycle although the latter effect is greatly reduced by use of a negative discharge circuit (end-of-line clipper) for the PFN as discussed earlier.

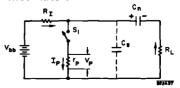

A simplified diagram of the PFN charging and regulating circuits is shown in Fig. 13-13 along with the pertinent waveforms. In the conventional method of regulation or de-Q'ing, the charging transformer is a single-winding inductor shunted by a parallel RC network in series with a switch, usually a thyratron tube. Because the charging inductor voltage rises to approximately twice that of the dc power supply, the tube, its filament and reservoir transformers, and the RC network all rise to a very high voltage above ground, requiring large insulators and component separation. It is also necessary to insulate the tube from its trigger circuitry. Space was not available for insulating these components to 45 kV, so the step-down transformer circuit of Fig. 13-13 was developed. An additional advantage of the low-voltage regulating circuit was that a solid-state switch could be employed, offering longer life and more trouble-free operation.

Figure 13-13 Pulse-forming network charging and regulating circuits with waveforms. Regulation occurs at  $t_0$ . Maximum silicon controlled rectifier switch current =  $nI_0$ , where n = 25.

The operation of either circuit is basically the same, the major difference being the leakage inductance present in the charging transformer. For the lossless (infinite Q) case, the charging current flowing into the PFN capacitors and the resultant voltages across the charging transformer primary and the PFN are given, respectively, by

$$i_{\rm PFN} = \frac{V_{\rm DC}}{\omega L_p} \sin \omega t \tag{13-3}$$

$$V_{L_p} = -L_p \frac{di_{PFN}}{dt} = -V_{DC} \cos \omega t \tag{13-4}$$

$$V_{\text{PFN}} = \frac{1}{C_{\text{PFN}}} \int_{0}^{t} i_{\text{PFN}} dt = V_{\text{DC}} (1 - \cos \omega t)$$

(13-5)

where  $\omega = (L_p C_{PFN})^{-1/2}$ , and  $L_p$  is the inductance of the charging transformer primary.

The charging current is restricted to a unidirectional flow by the presence of the charging diode and thus forms the basis for this method of regulation. If the current is forced to stop flowing into the PFN, then the voltage will remain at the level reached except for the small leakage present. This is accomplished by "loading" the charging transformer (or inductor) with a parallel resistor and capacitor. The voltage across the inductor then becomes a function primarily of its inductance, the magnitude of the current when the switch was

closed, and the added resistance and capacitance. Initially the uncharged capacitor in the secondary circuit appears as a short circuit and the voltage across the inductor drops to zero as shown in Fig. 13-13. It will then assume one of three possible forms, depending upon whether the R-L-C combination is overdamped, critically damped, or underdamped. Lowering the transformer primary voltage drop thus causes the anodes of the charging diodes to become negative with respect to their cathodes, and conduction ceases.

Considering the underdamped or damped oscillatory case with the resistance and capacitance reflected into the transformer primary, and assuming that current flow to the PFN is zero, the voltage across the inductance is given by

$$V_{L_p} = \frac{I_0}{\omega_0 C} \exp\left[-\frac{\omega_0 (t - t_0)}{2\omega_0 RC}\right] \sin \omega_0 (t - t_0)$$

(13-6)

where

$$\omega_0 = \left(\frac{1}{L_n C} - \frac{1}{4R^2 C^2}\right)^{1/2}$$

and

$$I_0 = \frac{V_{\rm DC}}{\omega L_p} \sin \omega t_0$$

that is,  $I_0$  is the magnitude of the charging current  $i_{PFN}$  at the instant of regulation ( $t_0$  in Fig. 13-13). This analysis has neglected any resistance in the charging transformer, wiring, or semiconductor switch as these would normally be so small as to have a negligible effect on the resultant voltage and would merely serve to complicate the calculation. It has also neglected transformer secondary leakage reactance as this is a small inductance and contains no initial stored energy. Equating the time derivative of Eq. (13-6) to zero indicates that  $V_{L_p}$  is maximum when  $2\omega_0 RC = \tan \omega_0 (t_1 - t_0)$ . The equation for  $V_{L_p}(\max)$  can then be written as follows:

$$V_{L_p}(\max) = I_0 R \left[ 2 \exp\left(-\frac{\omega_0(t_1 - t_0)}{\tan \omega_0(t_1 - t_0)}\right) \cos \omega_0(t_1 - t_0) \right]$$

$$= I_0 R[K_E]$$

(13-7)

where  $(t_1 - t_0)$  = the time required after  $t_0$  to reach  $V_{L_p}(\max)$ . The values of  $K_E$ , the bracketed expression of Eq. (13-7), can be calculated as a function of  $\omega_0(t_1 - t_0)$  and are given in Table 13-4.

Table 13-4 Values of  $K_E$  of Eq. (13-7) for different values of  $\omega_0(t_1-t_0)$

| $\omega_0(t_1-t_0)$ | Deg. | 30    | 35    | 40    | 45    | 50    | 55    | <b>6</b> 0 | 65    | 70    | 75    | 80    |

|---------------------|------|-------|-------|-------|-------|-------|-------|------------|-------|-------|-------|-------|

|                     | Rad. | 0.533 | 0.611 | 0.698 | 0.785 | 0.873 | 0.960 | 1.047      | 1.134 | 1.222 | 1.309 | 1.396 |

| $K_E$               |      | 0.688 | 0.684 | 0.666 | 0.645 | 0.618 | 0.583 | 0.545      | 0.496 | 0.438 | 0.364 | 0.281 |

From Eq. (13-7),

$$R = \frac{V_{L_p}(\text{max})}{I_0 K_E} \tag{13-8}$$

and from the maximization condition,

$$C = \frac{\tan \omega_0 (t_1 - t_0)}{2\omega_0 R}$$

(13-9)

To obtain the actual values required in the transformer secondary, R must be divided by the square of the turns ratio and C multiplied by this value. Since a damped oscillatory condition was chosen to insure  $i_{L_p}$  reaching zero before the start of the next charging cycle,  $\omega_0$  should be selected so that

$$\omega_0(t_3 - t_0) + \omega_0(t_1 - t_0) \ge \pi \tag{13-10}$$

The time between pulses for the fastest repetition rate should be used for  $t_3$ . If the repetition rate is lowered,  $t_3$  will increase and  $V_{L_p}$  and the switch current will have time to reverse unless the switch is unidirectional. The siliconcontrolled rectifier is essentially unidirectional except for a short turnoff or recovery time. From Eq. (13-6) it is clear that the lower the value of  $\omega_0 RC$ , the more damped will be the negative half-cycle of the waveform and, consequently, the less will be the strain on the switching device. The charging current, which was flowing through the transformer primary  $L_p$  to the PFN, is diverted to the RC network at  $t_0$ . For the conventional method with a single-winding inductor, it has the form:

$$i_{L_p} = I_0 \exp \left[ -\frac{\omega_0(t - t_0)}{2\omega_0 RC} \right] \frac{\sin[\omega_0(t - t_0) + \omega_0(t_1 - t_0)]}{\sin[\omega_0(t_1 - t_0)]}$$

(13-11)

This current has an initial value of  $I_0$  and then decays as a damped sinusoid with its phase and magnitude determined by the value of  $\omega_0(t-t_0)$ .

From the definition of  $\omega_0$ , Eq. (13-6),  $L_p$  must be less than  $4R^2C$  for the underdamped or oscillatory condition to exist. It should also be noted that  $L_p$  must be selected in conjunction with the total PFN capacitance so that sufficient time is allowed to dissipate the energy remaining in the charging transformer. Energy remaining at the beginning of the next charging cycle will result in the charging current starting at some nonzero value. This can result in transients in the circuit and will also cause the PFN to charge at a faster rate which will affect the recovery of the main thyratron. An additional term,  $\omega L_p I_{t_3} \sin \omega t$ , must be added to Eq. (13-5) as a result of the current still flowing at  $t_3$ .

The choice of  $V_{L_p}(\max)$  is somewhat arbitrary and depends upon the difference between the maximum PFN voltage (without de-Q'ing) and the desired regulated level of PFN voltage. This does not mean that regulation will cease for voltages even higher than the design maximum but, that under certain

circumstances, some charge may pass to the PFN with a resulting increase in voltage. Referring to Fig. 13-13, it is obvious that  $V_{L_p}$  should not be allowed to rise above the regulated value of  $V_{\rm PFN}$  for some allowable increase in  $V_{\rm DC}$ . The normal operating magnitude of  $V_{L_p}(\max)$  must be somewhat less than this. A value of  $V_{L_p}(\max)$  equal to approximately 25% of the power supply voltage  $V_{\rm DC}$  will provide for regulation over a considerable increase in voltage. The normal operating value of regulated PFN voltage is selected to take care of the maximum decrease expected in ac line voltage and should usually be set for a range of 3 to 5% regulation. Percentage regulation is here defined as follows:

% regulation =

$$\frac{V_{\text{PFN}}(\text{unreg}) - V_{\text{PFN}}(\text{reg})}{V_{\text{PFN}}(\text{unreg})} \times 100$$

(13-12)

It should be remembered that the greater the percentage regulation, the higher the power dissipation so that some discretion is necessary in making this choice. Another point to be considered is the "dead" region resulting with very low values of regulation; that is, where the time rate of change  $(dV_{\rm PFN}/dt)$  approaches zero. Most comparator circuits respond in proportion to this rate of change. This region of uncertainty in de-Q'ing performance cannot be accurately defined but measurements indicate that it includes values of regulation below about 0.25%.

To complete the selection of the two required parameters, resistance and capacitance, it now remains to discuss power dissipation and energy. A comparison between the inductive voltage and current, Eqs. (13-6) and (13-11), shows that the current leads the voltage by the angle  $\omega_0(t_1-t_0)$ . The current, therefore, reaches zero when  $\omega_0(t-t_0) + \omega_0(t_1-t_0) = \pi$  and the energy in the inductance becomes zero at the same time. The initial energy  $(\frac{1}{2}L_p I_0^2)$  is then stored in the capacitor, less the amount which was dissipated in the resistance. The current will try to flow in the reverse direction, with the voltage still positive across the switching device. The semiconductor switch will turn off when the current drops below a certain level, known as the holding current. A short recovery period or turnoff time is involved, but this is a matter of a few microseconds, approximately 25 in the large, high-current devices. The capacitive energy is then isolated from the inductance and is dissipated at a rate determined by the RC time constant, which is the same rate at which the damped voltage and current sinusoids were attenuated. In the actual circuit, a series RC protection against voltage spikes is placed across the switch so that a small amount of negative current continues to flow. The average power dissipated over the entire charging period is determined from the inductive energy as follows:

$$P = \frac{\frac{1}{2}L_p I_0^2}{t_3} = \frac{1}{2}(PRR)L_p I_0^2$$

(13-13)

where PRR is the pulse repetition rate.

The magnitude of  $I_0$ , as defined in Eq. (13-6), can also be calculated in terms of  $V_{PFN}$  and  $V_{DC}$  by combining Eqs. (13-3) and (13-5), in which case

$$I_0 = \left[ \frac{C_{\text{PFN}}}{L_p} V_{\text{PFN}} (2V_{\text{DC}} - V_{\text{PFN}}) \right]^{1/2}$$

(13-14)

where  $V_{PFN}$  represents the voltage at  $t_0$ , i.e., the regulated value.

So far, transformer leakage reactance has not been introduced into the analysis. The secondary leakage, which will be quite small for the low-voltage winding, has only a very minor effect on the regulation. Primary leakage inductance, on the other hand, contains energy due to the flow of charging current which is not extracted by the process of loading the secondary. The transformer should, therefore, be designed so that this leakage is as small as possible. The complexity of the circuit prevents an exact explanation of its behavior. In the first place, it was assumed that the semiconductor-charging diode was a perfect unidirectional switch and this is not exactly true—a recovery time of 10 to 15  $\mu$ sec is typical in medium-sized diodes. Second, the exact nature of the circuit is not known; only an approximate equivalent circuit can be considered. Referring to Fig. 13-13, the following simplified explanation can be given, again assuming that the charging diode ceases conduction at  $t_0$ . The primary leakage reactance will appear as a series inductance in the charging circuit, not shunted by the secondary resistance and capacitance, and having a stored energy of  $\frac{1}{2}L_L I_0^2$  joules. There is also a distributed capacitance,  $C_D$  in Fig. 13-11, from both primary and secondary to ground. This distributed capacitance on the primary side of the SLAC transformer is approximately 0.0025  $\mu$ F and can be considered in parallel with the de-Q'ing signal divider and, therefore, charged to a voltage  $V_{DC}$  at  $t_0$ . The  $R-L_n-C$  combination can be transformed approximately into a twoelement series equivalent circuit and, due to the low Q of the combination, one element will be a resistor of sizable value. The leakage inductance is. therefore, still contained in a closed path which will prevent an abrupt interruption of its current flow. If transferred directly to the distributed capacitance, the inductive energy would cause a voltage rise equivalent to  $I_0(L_1/C_D)^{1/2}$ . However, the derived low-Q, series R-L-C network results in a damped sinusoidal current which is initiated by an impulse function equal in magnitude to  $L_L I_0$ . The voltage which this current develops across the distributed capacitance is then superimposed on  $V_{L_n}$  of Fig. 13-13. It is considerably more damped than  $V_{L_n}$  and has a much higher frequency. Unfortunately, the exact magnitude of this voltage cannot be determined, but it could very well reach a value in excess of the regulated PFN voltage. It is, therefore, necessary to reiterate that the transformer leakage reactance should be as small as possible in order to minimize this voltage.

From the foregoing analysis, it is apparent that the entire design procedure is clouded with a certain degree of arbitrariness. Furthermore, the complexity of the equations encountered, even after simplifying assumptions are made, makes a rigorous generalized analysis of the circuit impossible. Some

insight into the problems involved, though, and a knowledge of the general approach will aid considerably in performing the circuit design.

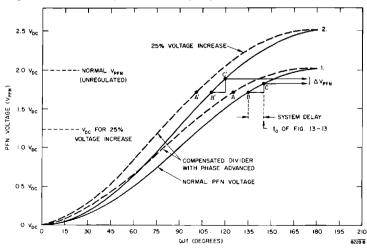

The de-Q'ing signal divider plays an important part in the accuracy obtained. Accuracy is best described as percentage error and is defined as follows:

$$% error = \frac{\Delta V_{PFN}(reg)}{V_{PFN}(t_0)} \times 100$$

(13-15)

Certain fixed delays are inherent in the system, both in the comparator and trigger circuits and in the turn-on time of the semiconductor switch. The turn-on time is typically 10  $\mu$ sec or more for high-current devices although the exact definition of full turn-on may vary somewhat. The delay in the comparator and trigger generator depends upon the circuit used and is not necessarily constant for different percentages of regulation. For a high degree of accuracy, the desired level of the attenuated  $V_{\rm PFN}$  waveform must be compared to a very stable, highly regulated dc voltage. For small percentages of regulation, near its maximum value, the time rate of change of this voltage is very small, and the rise time of the comparator output pulse may be greater than it would be with a faster rising input signal. Nevertheless, a certain delay does exist, and assuming that it is fixed, the result of it can be seen by studying Fig. 13-14.

The solid line of waveform 1 represents a normal-amplitude PFN voltage. The command to commence regulation is given at point B, and it is assumed that the de-Q'ing signal divider is exactly compensated (zero phase shift) and the system requires about 10° delay, an exaggerated figure for the purpose of illustration. Therefore, 10° later the regulation process is complete, and the PFN voltage is set at the level represented by C. Next, consider a cycle in

Figure 13-14 Compensated de-Q'ing signal divider waveforms.

which all conditions remain the same but a 25% increase in unregulated PFN voltage occurs as represented by waveform 2. The command to regulate, now B', is given at the same voltage level although occurring earlier in time. The regulated level, again reached after a  $10^{\circ}$  delay, is set at C'. It is readily seen that this latter level represents an increase over the value attained with normal voltage, and this increment is identified as the numerator of Eq. (13-15). The denominator is taken as point C which represents  $t_0$  of Fig. 13-13.

If the waveform from the de-Q'ing signal divider is now advanced in phase by the required amount, the commands to regulate are given at points A and A' for the normal and increased PFN voltage, and the regulation occurs at points B and B'. These points now represent the same level of voltage, and the regulation is ideal; that is, the percentage error is zero. It should be noted that if the phase were advanced further, so that overcompensation existed, the regulated value of the increased voltage would be less than for the normal voltage.

To calculate the phase shift associated with the divider network, consider a divider consisting of n identical sections of  $R_1$  and  $C_1$  and an output section of  $R_2$  and  $C_2$ . This results in n+2 simultaneous integral equations and, if driven by the PFN voltage of Eq. (13-5), the solution for the output voltage across  $R_2$  is represented by the following equation. For  $V_{in} = V_{DC}(1 - \cos \omega t)$ ,

$$V_{\text{out}} = V_{\text{DC}} \frac{R_2}{nR_1 + R_2} \left[ 1 - K_1 \cos(\omega t + \theta) + K_2 e^{-t/\tau_p} \right]$$

(13-16)

where

$$\theta = \tan^{-1} \frac{\omega(\tau_1 - \tau_p)}{\omega^2 \tau_1 \tau_p + 1}$$

$$\tau_p = \frac{nR_1 R_2}{nR_1 + R_2} \left( \frac{C_1}{n} + C_2 \right) \approx R_2 C_2$$

$$\tau_1 = R_1 C_1$$

$$K_1 = \left[ \frac{\omega^2 \tau_1^2 + 1}{\omega^2 \tau_p^2 + 1} \right]^{1/2}$$

$$K_2 = \frac{\omega^2 \tau_p (\tau_1 - \tau_p)}{\omega^2 \tau_p^2 + 1}$$

An examination of this expression indicates that it reduces to the input waveform, reduced by the resistive ratio, when  $\tau_1$  equals  $\tau_p$ . For a constant phase shift, which is necessary for the greatest accuracy, the last term in the equation should be zero. Although this is not possible, the term will essentially vanish after five time constants so that the earliest reference to the waveform should be made after a time  $\geq 5\tau_p$ . In calculating  $R_2$  and  $C_2$ , consideration must be given to the input resistance and capacitance of the comparator circuit and any cable capacitance between the divider and comparator. The choice of  $R_1$  in

high-voltage circuits must take into consideration power dissipation and voltage rating, in conjunction with the desired time constant, and the number of sections required is determined by these factors. The resistors must also be noninductive with low temperature and voltage coefficients and low thermal noise. A further consideration is corona, which is associated with circuits operating above approximately 30 kV. This may make it necessary to immerse the divider in oil, as was the case with SLAC modulators. As the system time delay is never known exactly when the original modulator design is made, the practical approach is to calculate the resistors and  $C_1$  and then adjust  $C_2$  for best regulation when the circuit is tested.

The final selection to be made is the choice of semiconductor switch. This requires a knowledge of the maximum voltage to be expected across the device and the average and rms currents. Root-mean-square current is not easily determined but can be approximated closely enough for practical purposes by calculating the current for the much simpler case when the system is critically damped and  $\omega_0$  is zero. This results in

$$I_{\text{switch}}(\text{rms}) \approx I_0 \left(\frac{(\text{PRR})L_p}{1.6R}\right)^{1/2}$$

(13-17)

where R is the secondary resistance for the transformer-coupled circuit. Average current can be calculated by an integration of Eq. (13-11) and is accomplished by referring this current to the transformer secondary to give the following form:

$$i_{\text{switch}} = \frac{nI_0 \exp\left[-\frac{\omega_0(t - t_0)}{2\omega_0 RC}\right] \sin[\omega_0(t - t_0) + \omega_0(t_1 - t_0)]}{\sin[\omega_0(t_1 - t_0)]}$$

(13-18)

and

$$I_{\text{switch}}(\text{AV}) = \frac{(\text{PRR})}{\omega} \int_{0}^{\pi - \omega_0(t_1 - t_0)} i_{\text{switch}} d(\omega_0 t)$$

(13-19)

The upper limit of integration is obtained by solving Eq. (13-18) for the angle  $\omega_0(t_2-t_0)$  at which the switch current becomes zero. This will always be in the second quadrant and can, therefore, be written as  $\omega_0(t_2-t_0)=\pi-\omega_0(t_1-t_0)$ . The lower limit is identified as the angle  $\omega_0 t_0$  when the de-Q'ing circuit is fired and represents zero on the  $\omega_0 t$  angular scale. Inserting Eq. (13-18) in Eq. (13-19) and carrying out the integration yields

$$I_{\text{switch}}(\text{AV}) = (\text{PRR})nI_0(L_p C_{\text{PFN}})^{1/2} \left\{ \exp\left[ -\frac{\pi - \omega_0(t_1 - t_0)}{\tan \omega_0(t_1 - t_0)} \right] \right.$$

$$\times \sin \omega_0(t_1 - t_0) + \sin 2\omega_0(t_1 - t_0) \right\}$$

(13-20)

where n is the charging transformer turns ratio. The value of the term in braces  $\{K_I\}$  is evaluated in Table 13-5, using the same values of  $\omega_0(t_1 - t_0)$  as in Table 13-4.

Table 13-5 Values of  $K_I$  of Eq. (13-20) as a function of  $\omega_0(t_1-t_0)$

| $\omega_0(t_1-t_0)$ | Deg. | 30    | 35    | 40    | 45    | 50    | 55    | 60    | 65    | 70    | 75    | 80    |

|---------------------|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|                     | Rad  | 0.533 | 0.611 | 0.698 | 0.785 | 0.873 | 0.960 | 1.047 | 1.134 | 1.222 | 1.309 | 1.396 |

| $K_{I}$             |      | 0.871 | 0.955 | 1.020 | 1.066 | 1.100 | 1.118 | 1.124 | 1.122 | 1.109 | 1.091 | 1.066 |

The triggered semiconductor devices, commonly known as silicon controlled rectifiers and Trinistor controlled rectifiers, are available with current ratings up to approximately 500 A rms and voltages of 1200 V and more. The transformer turns ratio, in conjunction with the PFN voltage and current, determine the operating conditions for the switch. It should be remembered that, as a rule, the higher the current rating, the slower the turnon time; and forcing a fast-rising current through the switch before it is fully turned on will create excessive peak power dissipation. Another precaution to be observed concerns high-voltage transients, which are prevalent in pulse modulators.\* A series RC network across the switch affords protection against such voltage spikes. If the choice between series and parallel operation of switches arises, the series connection appears to be preferable. This requires a voltage-dividing network across the two devices but ensures that the current rate-of-rise through each one is very nearly equal. Parallel operation, unless the devices are very closely matched, usually requires current-equalizing elements which are located in series with the individual switches. Furthermore, even though originally matched, it is not assured that they will remain so during their lifetime. In calculating the currents for selection of the switch, the worst-case conditions should be considered, that is, the fastest repetition rate and greatest percentage regulation that the circuit will be subjected to.

In the SLAC system, the dc reference voltage controls both the output of the ac induction regulators and the level at which PFN regulation occurs. This ensures that the percentage regulation remains about constant for any set input voltage level. The reference power supply is regulated to better than 0.01% against line and load changes and has a maximum peak ripple of 0.7 mV. This is further attenuated in the comparator to less than 0.03 mV. Regulation errors as small as 0.045% have been achieved without making a concentrated effort to reach the minimum possible. This represents a change of approximately 110 V in the 250-kV klystron pulse.

Some specific data on the de-Q'ing components used in the SLAC modulators are as follows:

CHARGING TRANSFORMER—25:1 step-down ratio.

Primary: 1.8 H inductance, 25 mH leakage inductance referred to primary, 5.7 ohms resistance.

Secondary: 0.03 ohm resistance, isolated from the primary by a grounded electrostatic shield.

<sup>\*</sup> One such voltage spike, which can be particularly harmful to the semiconductor switch, is described in the section on despiking networks.

RESISTOR—2 ohms, 8 kW. Eight 0.25-ohm, 1000-W edgewound ribbontype resistors in series.

CAPACITOR—50  $\mu$ F, 660 V rms. Two 25  $\mu$ F ac motor-run capacitors in parallel.

SEMICONDUCTOR SWITCH—Type 2N3895 controlled rectifier, 1200 V, 175 A average, 275 A rms. Two series-connected units with voltage dividing networks across each. A series despiking network, 0.5 µF capacitance and 25 ohm resistance, connected across the combination.

The transformer-semiconductor circuit offers two distinct advantages over the conventional method of regulation. The components are operated at relatively low voltage which requires much less space for insulation and the low-voltage components are generally smaller. The life of the controlled rectifier far exceeds that of gaseous tubes. An accurate projection of the life-time cannot be made at this time; however, some of the devices at SLAC have now accumulated approximately 9000 hours operating time.

# Despiking network (WTT)

The function of the despiking network is to protect the charging transformer from excessive voltage spikes and the charging diodes from excessive peak current when the main thyratron fires. The following explanation refers to the simplified schematic diagram of Fig. 13-11. The network is shown mounted in the modulator in the photograph of Fig. 13-12.

The charging transformer (or inductor) has an inherent distributed capacitance,  $C_D$ , to ground. For simplicity, this is shown as a lumped capacitance although the actual equivalent circuit is of a more complicated nature. This capacitance is charged to approximately  $V_{\rm DC}$  when the main thyratron fires. The exact value will depend upon whether the de-Q'ing cycle is complete. If it is, then the voltage reached will be  $V_{\rm DC}$  plus  $V_{L_p}$  as shown in Fig 13-13. In the absence of the de-Q'ing, the value reached will depend upon whether  $C_D$  in conjunction with the charging transformer and filter capacitance has had time to reach a stabilized condition after the PFN current has stopped flowing.

When the main thyratron fires and the PFN has discharged, which is approximately 3.5  $\mu$ sec later in the SLAC modulators, the PFN is left with a small positive potential and the thyratron remains in the conducting state. This is owing to the fact that the characteristic impedance of the PFN is purposely made slightly smaller than the reflected impedance of the klystron. Referring to Fig. 13-11, it is seen that a conduction path then exists from  $C_D$  through the charging diodes, the PFN, and the thyratron back to  $C_D$ . Most of the PFN inductance will be bypassed by its capacitance so that only one section of the inductance of each network is in the circuit. A rather complicated parallel path also exists through the PFN and the pulse transformer primary, although the inductance of the transformer is large enough to prevent a fast-rising current from flowing through this circuit. As the resistance of the conduction path is very low, being mostly the forward resistance

of the charging diodes, the peak current in the absence of a despiking network can reach magnitudes of many hundreds of amperes. This current, on a repetitive basis, would normally far exceed the surge current rating of the charging diodes.

Because of this current flow, the charge on  $C_D$  reverses and the voltage becomes very nearly  $-V_{DC}$ . The frequency of the waveform is a function of the equivalent series inductance and capacitance of the circuit and is approximately 500 kHz in the SLAC modulators without the despiking network. This high-frequency waveform creates excessive turn-to-turn and layer-to-layer voltages on the PFN side of the charging transformer. It is also transferred to the secondary and appears as a reverse voltage across the semiconductor switch. The ideal remedy would be a low-pass filter which offers no attenuation to the PFN charging frequency but presents very high attenuation to the high-frequency waveform. Such a filter is best approximated by a parallel LR network in series with the charging circuit as shown in Fig. 13-11. If L is some small percentage of the charging transformer primary inductance, it will have little effect on the PFN charging waveform other than to lower the frequency slightly. The resistance is selected to have a value which is much higher than the reactance of L at the charging frequency and yet lower than the reactance at the high frequency discussed above. The equivalent series network will then appear as an inductance to the charging frequency and as a resistance in series with a smaller inductance at the high frequency.

A lumped capacitance analysis of the circuit does not yield results which are useful in the design of the network. An empirical approach, used with a knowledge of the circuit behavior resulting from the added elements, is the most practical design procedure. The resistance, which serves to attenuate the high-frequency current and dissipate the energy initially stored in  $C_n$ , should be as large as possible. However, a large resistance requires a very large value of inductance as its reactance must be much greater than the resistance to allow most of the high-frequency current to flow through the resistor. From the standpoint of the PFN charging circuit and also the de-Q'ing circuit, the inductance should be as small as possible. The choice of L, then, involves attempting to satisfy these two opposing requirements. A compromise is possible because the two frequencies are generally separated by two to three decades. Experience indicates that a value of inductance in the range from 0.05 to 1.0% of the charging transformer inductance will provide a network with considerable attenuation to the high-frequency waveform. The frequency will also be lowered by the impedance of the added circuit. The resistance is selected by trial to give minimum negative voltage,  $-V_{C_n}$ , at the charging transformer.

The following data on the SLAC network illustrates the variation of  $V_{C_D}$  with resistance under operating conditions:

3000 R(ohms)250 500 1000 1500 2000 2500 3500 4000  $-V_{c_n}(kV)$ 25 20 8 8 9 11 8 11 12 For this test, the dc power supply voltage was 20 kV, the charging transformer primary inductance was 1.8 H, the transformer distributed capacitance,  $C_D$ , was 0.0025  $\mu$ F, and the despiking inductance, L, was selected to be 15 mH or 0.83% of the charging transformer inductance. It is seen that the negative voltage rises rapidly for resistances less than optimum. Also of interest is the minimum value of negative voltage obtained with four different designs of essentially the same charging transformer, each enclosed in an oil-filled case of approximately the same size. The dc power supply voltage was again 20 kV, when the following comparative data were taken:

| $C_D$ ( $\mu$ F)    | 0.0007 | 0.0025 | 0.005 | 0.0185 |

|---------------------|--------|--------|-------|--------|

| $oldsymbol{L}$ (mH) | 19.5   | 15     | 19.5  | 11.5   |

| R (ohms)            | 3000   | 2000   | 900   | 250    |

| $-V_{c_D}(kV)$      | 9      | 8      | 11.4  | 15.75  |

The range of distributed capacitance varies by a factor of 26 to 1, and the minimum negative voltage obtainable increases with the capacitance. This indicates that the capacitance should be kept reasonably small. The smaller capacitance will also reduce the high-frequency current that must flow through the charging diodes. Furthermore, it will reduce the stored energy, some of which is dissipated with a consequent reduction of the modulator efficiency.

## Switch tubes (RWB)

Early in 1963, efforts were concentrated upon the evaluation of hydrogen thyratrons for the SLAC modulators, because spark gaps and ignitrons did not meet system requirements.

No single hydrogen thyratron which would meet all the SLAC specifications was available, so the modulators were constructed to permit the use of hydrogen thyratrons known to exist at that time, including two of the smaller tubes in a parallel PFN configuration. The two-tube system was used for initial beam tests in Sectors 1 and 2 and, in some modulators, during full beam operations for over a year with good performance.

SPECIAL SLAC REQUIREMENTS. The most stringent requirements imposed upon the SLAC thyratron centered around the anode delay time, variation (variation in switching time from minimum voltage and pulse rate to maximum voltage and pulse rate), instantaneous starting at full voltage, and long mean time between faults.

The variation in delay time through the SLAC modulators is an important parameter because it is desirable to utilize as much of the flat-top portion of the pulse as possible for beam acceleration.

The instantaneous start requirement is necessary because it would be impracticable to spend extra time varying operating voltages to get modulators back on whenever a fault occurred.

Table 13-6 Hydrogen thyratron specifications

| <del></del>                                     |                             |

|-------------------------------------------------|-----------------------------|

| Peak anode forward voltage $(e_{py})$           | 46 kV (max)                 |

| Peak anode inverse voltage $(e_{px})$           | 5 kV (max)                  |

| Pulse duration $(T_p)$                          | 4 μsec (max)                |

| Peak anode current $(i_b)$                      | 4000 A (max)                |

| Average anode current $(I_b)$                   | 5 A (max)                   |

| Rms anode current $(i_p)$                       | 140 A (max)                 |

| Anode delay time $(T_{ad})$                     | 0.4 $\mu$ sec (max)         |

| Anode delay time jitter $(T_I)$                 | 0.01 µsec (max)             |

| Anode delay time drift ( $\Delta T_{ad}$ )      | $0.04\mu\mathrm{sec}$ (max) |

| Anode delay time variation ( $\Delta T_{adv}$ ) | $0.15\mu\mathrm{sec}$ (max) |

| Anode dissipation factor $(P_b)$                | 70 × 10° (max)              |

| Pulse repetition rate (PRR)                     | 60 to 360 pulses/sec        |

| Number of kickouts                              | 4 (max )in 96 hours         |

| Operating life (objective)                      | 10,000 high-voltage hours   |

The long mean time to fault is required for beam stability. There are 245 modulators in the accelerator and even at four faults per 96 hours, which is the maximum fault rate specified, the mean time to fault for all the tubes in the accelerator would be approximately 6 min.

The principal specifications for the hydrogen thyratrons are shown in Table 13-6.

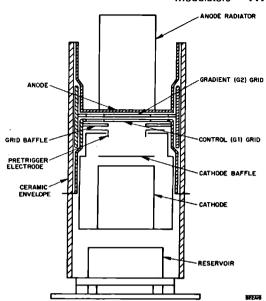

In order to meet the SLAC specifications the manufacturers incorporated a pretrigger electrode and modified the grid and baffle configurations for optimum switching time and low kickout rate.

PRETRIGGER ELECTRODE. The maximum anode delay in the hydrogen thyratron is largely determined by the time it takes the plasma in the relatively large cathode region to build up to a critical density in the control grid aperture region. When this point is reached, the tube begins to conduct. In order to reduce the ionization build-up time in the cathode region, a pretrigger electrode was installed between the cathode and the control grid (see Fig. 13-15). This electrode is connected to the trigger transformer through a 250-ohm resistor. The control grid is connected to the trigger transformer through an LC filter network. There is a delay through this network of approximately 0.1 µsec which allows current to flow to the pretrigger electrode and partially ionize the cathode region prior to application of the grid trigger. This mode of operation reduces the cathode ionization time from approximately 600 to 230 nsec and reduces the cathode ionization time variation from a nominal 350 to 100 nsec.

KEEP-ALIVE OPERATION. During the development phase, experiments were done with a constant dc voltage applied to the pretrigger electrode. The effect of the keep-alive voltage was to reduce the ionization time in the cathode

Figure 13-15 Typical SLAC hydrogen thyratron, showing grid structure and pretrigger electrode.

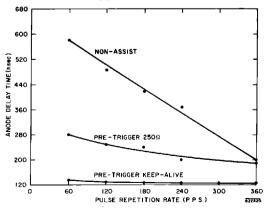

1 to approximately 80 nsec and the cathode ionization time variation to 1an 10 nsec. The effect of the three trigger modes on anode delay time can in Fig. 13-16.

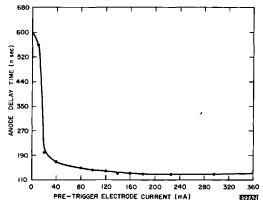

s can be seen in Fig. 13-17, the anode delay time is essentially stable 180 mA of keep-alive current on a new tube and is stable above 200 mA bes with 7000 hours, or more, of operation. About 2A through this

Figure 13-16 Anode delay time vs repetition rate for three trigger modes.

Figure 13-17 Anode delay time vs pretrigger electrode current.

electrode are required to fire the tube. It was decided to run the SLAC thyratron at a keep-alive current of 350 mA.

An additional benefit from operation of these tubes in the keep-alive mode was a marked increase in operating life. It is believed that a 3–5 times increase might be expected for a tube in this power class.

In order to help the manufacturers meet specifications, the effects of varying element spacings were studied at SLAC, and it was possible to correlate the delay times attributed to the different electrodes in the thyratron with tube dimensions. Several tubes with varying dimensions were built so that these effects could be studied. Manufacturing tolerances were minimized through direct measurements of interelectrode spacing from x-ray prints using high-energy, cobalt-60, x-ray techniques. It was noted for instance<sup>2</sup> that the spacing between the control grid G<sub>1</sub> and the cathode baffle was most critical (being the longest portion of the discharge path). The separation also varied critically with the focusing effect of the cathode aperture. A change of 0.020 in. (10%) in some cases accounted for delay changes of 170 nsec through this space. It was found that a spacing between 0.170 and 0.200 in. for a given cathode aperture was satisfactory for one type tube. The effect of G<sub>1</sub> to G<sub>2</sub> (gradient grid) spacing was studied, and a spacing of 0.125 to 0.135 in. was found to be optimum. Greater spacings produced greater delay time in G<sub>1</sub> to G<sub>2</sub> transfer which was probably due to the reduced field intensity or penetration in the  $G_1$  slot. Closer spacing than 0.120 in. produced excessive kickouts. The anode to G<sub>2</sub> spacing was optimized between 0.115 and 0.120 in. Larger spacings produced excessive time delay. Spacings less than 0.115 in. caused arcing and kickouts. Of course, the dimensions vary for other tube types, but the effects are the same.

CIRCUIT CONSIDERATIONS AFFECTING THYRATRON OPERATION. In order to achieve good performance and long life, it was necessary to tailor the modulator circuit and operating conditions to the tube. Two important thyratron

characteristics affecting the modulator design are recovery time and anode delay time stability. Also, the PFN charging circuit affects switch tube recovery. As slow a charging rate as possible was allowed, consistent with ability to de-Q the charging transformer at the highest repetition rate. Even so, the charging current does not start at zero, which has the effect of reducing recovery time from 300 to 225  $\mu$ sec.

The end-of-line clipper protects the switch tube and modulator from high inverse voltages due to load arcing and also has a pronounced effect on the normal inverse recovery voltage.

The thyratron trigger affects the anode delay time. A high amplitude trigger from a low impedance source reduces anode delay time. It was found that about 2000 V from a 25-ohm source was adequate.